# CONCOMPOSITION CONTRACTOR CONTRAC

Volume 26 Issue 3 APRIL / MAY 2020

🔰 @compoundsemi

www.compoundsemiconductor.net

Stacking unites GaN with silicon CMOS technology

# Breaking records with gallium oxide transistors

# Laying the foundations for GaN CMOS

Slashing substrate costs for multi-junction cells

Designing MMICs for millimetre-wave ICs

Oxford Instruments

Plasma processing solutions

# Best performance for next generation SiC power electronics to address global mega trends

RIXTRON

# AIX G5 WW C

Electric vehicles: on board chargers, power inverters

- Infrastructure: charging stations

- Renewables: solar and wind

- Industrial: motor drives, power supplies

- Power distribution: HVDC

Discover our SiC epi production batch tool with single wafer performance

info@aixtron.com www.aixtron.com

# Viewpoint

By Dr Richard Stevenson, Editor

# **Generating GaN CMOS**

THE COVID-19 epidemic is having a massive, global impact. It has already claimed tens of thousands of lives and forced many of us to adhere to a variety of social distancing measures, such as working from home and only leaving the house for essentials.

Until this epidemic is brought under control, it is unthinkable to host a global conference. It is for that reason that CS International has been rescheduled for November – although, to maintain communication and the flow of information within our community, we are also hosting a free, online summit on Tuesday 19 May (see page 13 for details).

A report on CS International would often be found within the pages of the April & May edition. But due to its absence this year for the reasons just outlined, there is more space in this issue to devote to a particular technology. And as you'll see, here you'll find detailed coverage of the development of the GaN IC.

The tremendous attributes of GaN and its related alloys – such as its ability to withstand high electric fields, its high saturation velocity that aids high-frequency operation, and its low on-resistance that leads to low switching losses – are driving its deployment in power electronics, communication and radar.

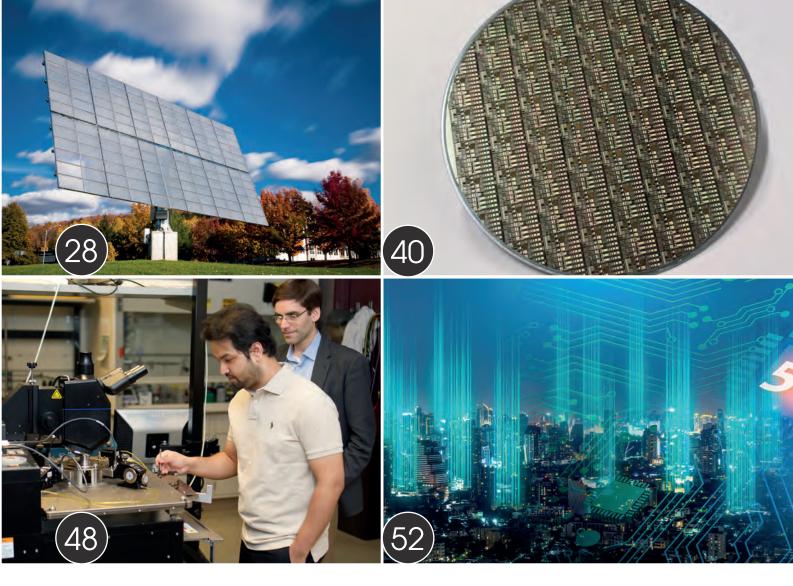

However, GaN has its weaknesses. High-performance *p*-type GaN FETs are challenging to produce, hampering the development of a GaN CMOS technology that will allow GaN power transistors to switch at far higher frequencies. Addressing this issue is critical, as it will allow circuit efficiency to increase in power supplies, while slashing the size and weight of passive components.

Offering one route to realising these gains are a team at MIT that has developed aggressively scaled FETs that feature a two-dimensional hole gas to provide carriers (see p. 46).

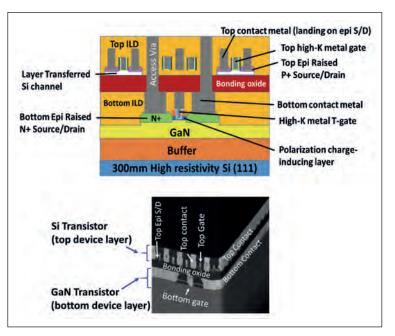

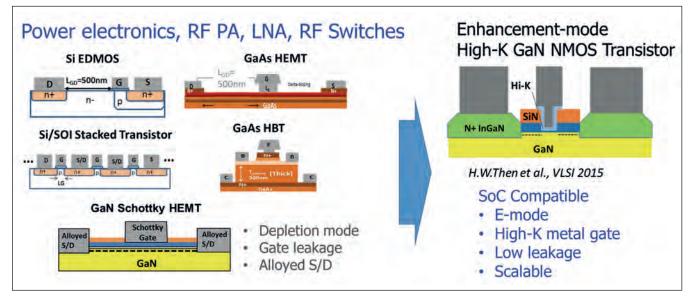

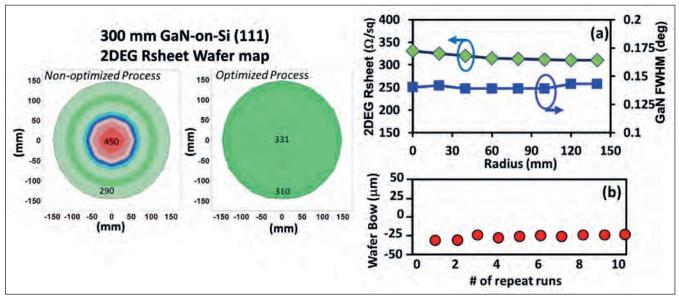

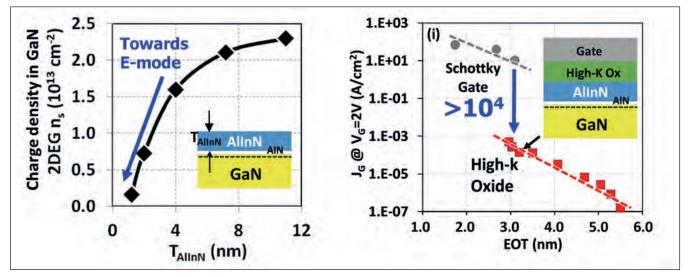

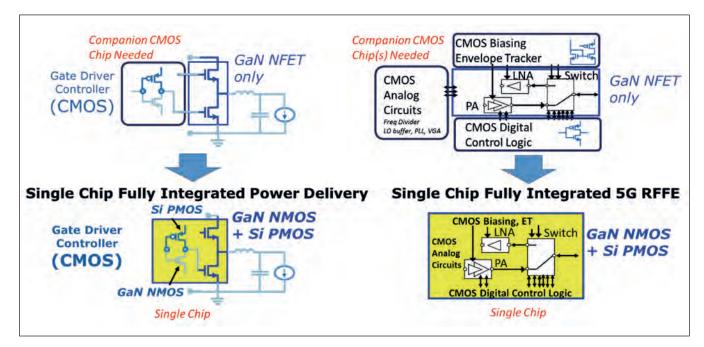

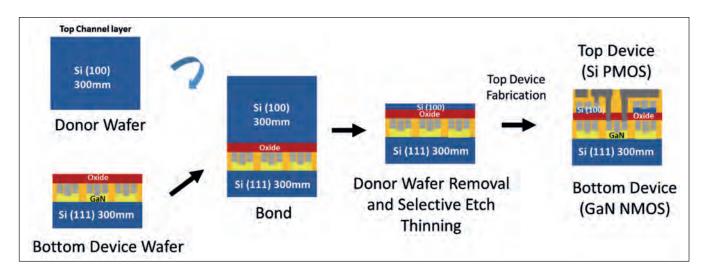

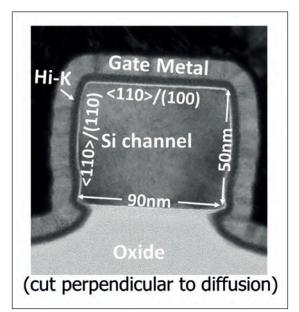

Working with this team, and a group at Cornell, are researchers at Intel. They reason that a good stepping stone to an all GaN CMOS technology is to unite GaN NMOS with high- $\kappa$  metal gate silicon PMOS. To accomplish this, they stack GaN and silicon transistors on 300 mm silicon wafers using a three-dimensional layer transfer process (see p. 32).

At imec, the microelectronics research centre in Belgium, they are adopting a different approach to making a *p*-FET. Rather than tackling the problem head-on, they are turning to a single-transistor invertor with a resistive load (see p. 40). Another feature of their work is the use of a buried oxide layer on a silicon-on-insulator substrate to ensure electrical isolation between different modules.

I encourage you to read about this breakthroughs at imec, plus those at Intel and MIT, while also participating in our on-line summit. As well as the insight you'll gain, it could play a part in helping you to feel connected during this outbreak.

| Editor Richard Stevenson                                              | richardstevenson@angelbc.com                       | +44 (0)1291 629640 | Circulation Director Scott Adams                                                                                                                                        | scott.adams@angelbc.com       | +44 (0)2476 718970          |

|-----------------------------------------------------------------------|----------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------|

| Contributing Editor Rebecca Pool<br>News Editor Christine Evans-Pughe | editorial@rebeccapool.com<br>chrise-p@dircon.co.uk |                    | Chief Executive Officer Stephen Whitehurst                                                                                                                              | stephen.whitehurst@angelbc.co | om +44 (0)2476 718970       |

| Sales Executive Jessica Harrison                                      | jessica.harrison@angelbc.com                       | +44 (0)2476 718970 | Joint Managing Director Sukhi Bhadal                                                                                                                                    | sukhi.bhadal@angelbc.com      | +44 (0)2476 718970          |

| USA Representatives Brun Media                                        |                                                    |                    | Joint Managing Director Scott Adams                                                                                                                                     | scott.adams@angelbc.com       | +44 (0)2476 718970          |

| Tom Brun                                                              | tbrun@brunmedia.com                                | +001 724 539-2404  | Directors Jackie Cannon, Sharon Cowley                                                                                                                                  |                               |                             |

| Janice Jenkins                                                        | jjenkins@brunmedia.com                             | +001 724-929-3550  | Published by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road,<br>Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com |                               |                             |

| Publisher Jackie Cannon                                               | jackie.cannon@angelbc.com                          | +44 (0)1923 690205 |                                                                                                                                                                         |                               |                             |

| Director of Logistics Sharon Cowley                                   | sharon.cowley@angelbc.com                          | +44 (0)1923 690200 |                                                                                                                                                                         |                               | _                           |

| Design & Production Manager Mitch Gaynor                              | mitch.gaynor@angelbc.com                           | +44 (0)1923 690214 |                                                                                                                                                                         |                               | When you have finished with |

Compound Semiconductor is published eight times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air maii), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2020. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, is published 8 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November/ December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CVS oSP UK. The 2020 US annual subscription price is \$198. Airfreight Hand mailing in the USA by agent named Air Business Ltd, c/o WN Shipping USA, 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Periodicals postage paid at Jamaica NY 11431. US Postmaster: Send address changes to Compound Semiconductor, Air Business Ltd, c/o WN Shipping USA, 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Printed by: The Manson Group. ISSN 1096-598X (Print) ISSN 2042-7328 (Online) © Copyright 2020.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time or the original publication. When companies and/or other changes their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise.

# CONTENTS

# 16COVER STORY A knowledgeable, responsive partner for plasma technologies

Shipments of Oxford Instruments Plasma Technology's deposition and etch tools are rising, due to their deployment in critical processes used for chip manufacture in growing markets

# 22 AFRL: Breaking records with gallium oxide

Engineers at the US Air Force Research Laboratory are propelling the performance of gallium oxide devices to new highs, by realising record-breaking critical field strengths and making the first FETs with switching losses below those for silicon

# 28 Slashing substrate costs for CPV

Switching to a silicon foundation and re-using germanium substrates offer two options for driving down the cost of multi-junction cells

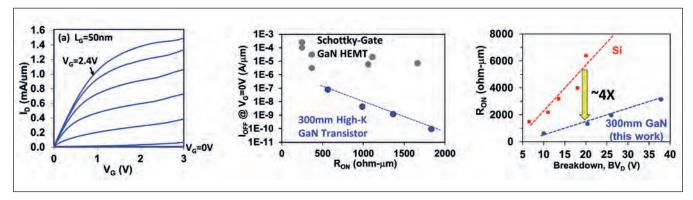

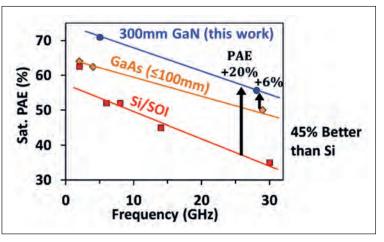

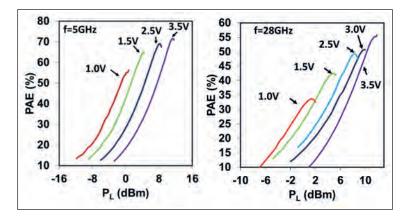

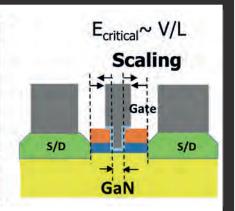

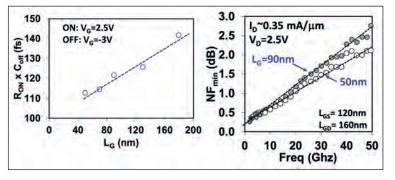

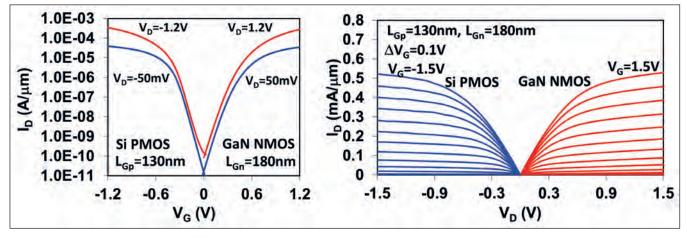

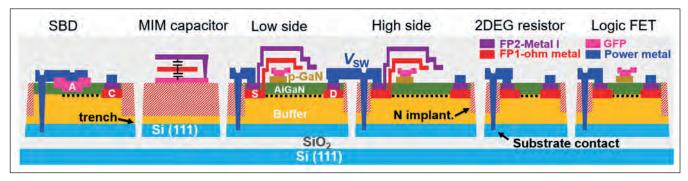

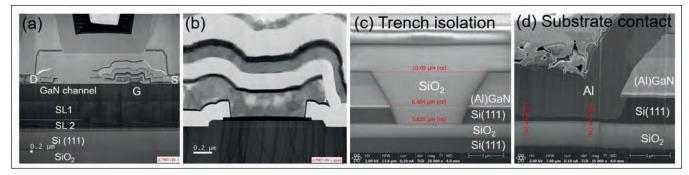

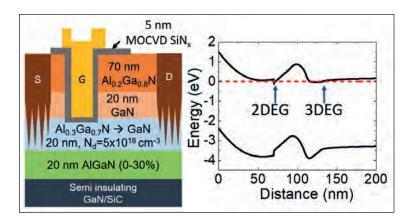

# 32 Stacking GaN and silicon transistors on 300 mm silicon

Next-generation mobile devices, data infrastructure and communication networks could be aided by three-dimensional, monolithic integration of GaN and silicon CMOS on 300 mm wafers

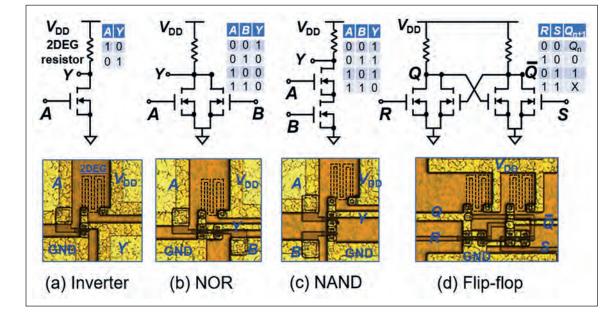

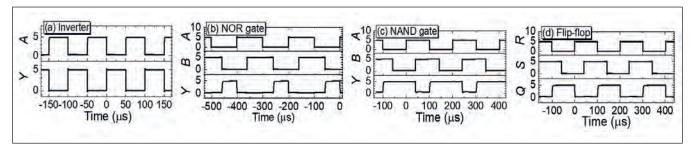

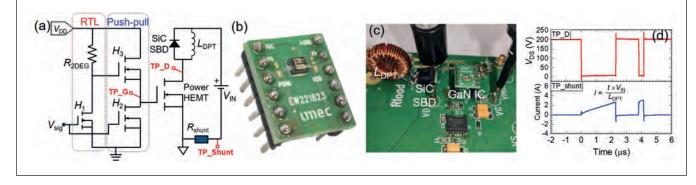

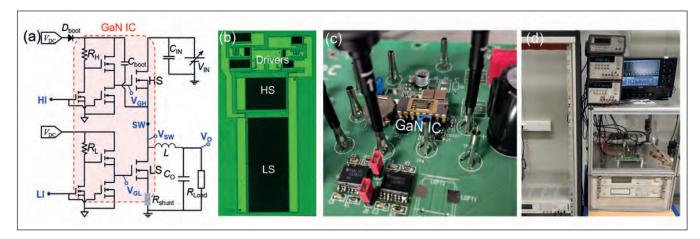

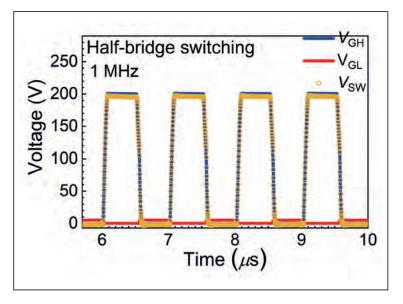

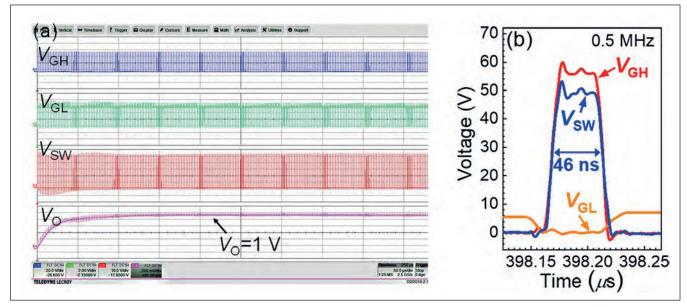

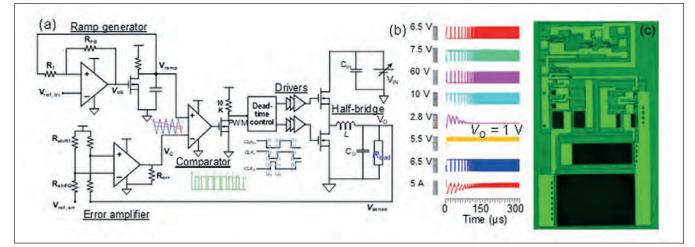

# 40 Monolithically integrated GaN power ICs

A demonstration of half-bridges and single-stage buck converters takes GaN power ICs another step forward

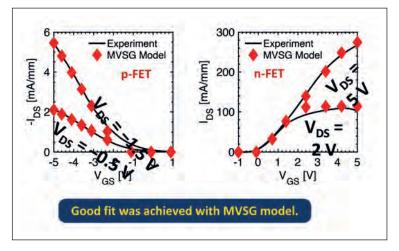

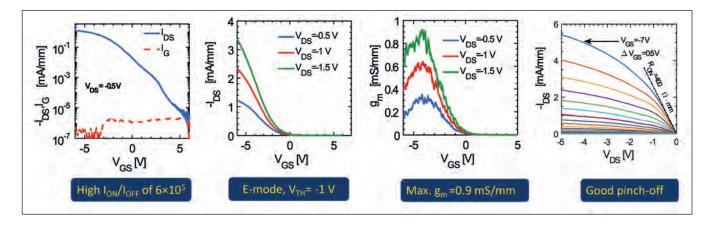

# 46 Getting ready for GaN CMOS

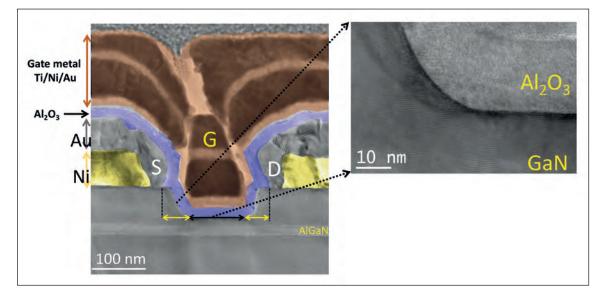

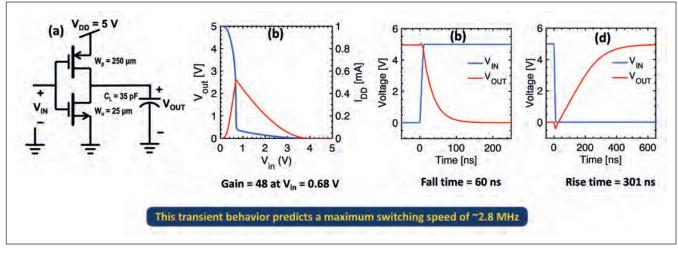

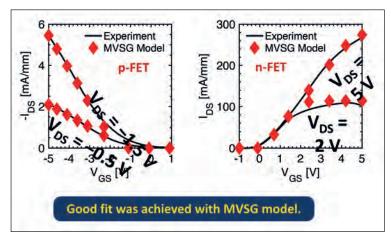

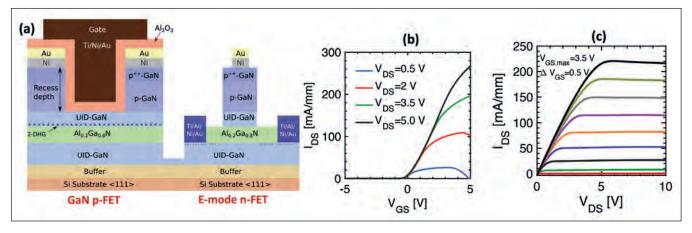

Aggressively scaled *p*-channel GaN transistors, formed on the same epiwafers as their *n*-type cousins, offer a very promising route to power electronic circuits made with a CMOS technology

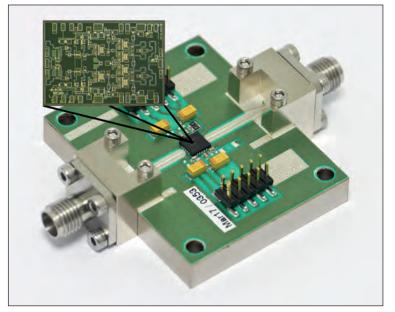

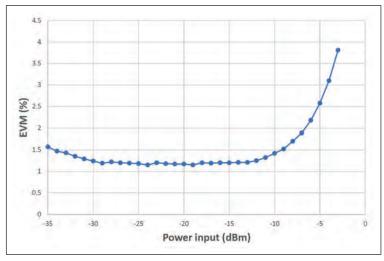

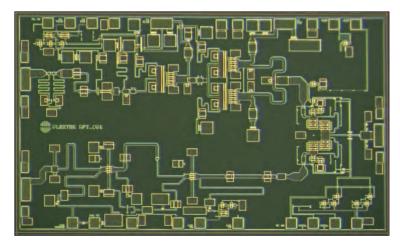

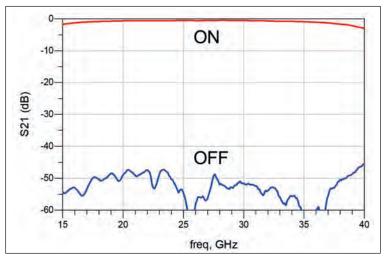

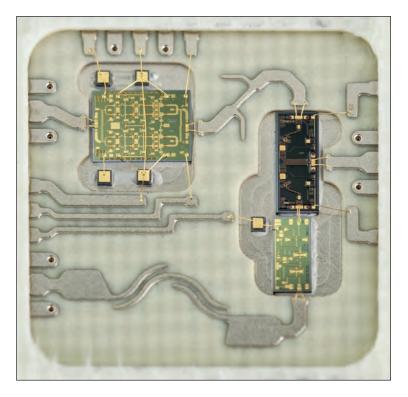

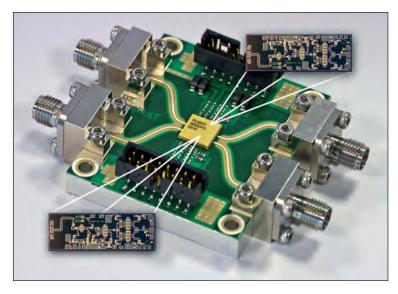

# 52 Designing MMICs for millimetre-wave 5G

High-performance front-ends for millimetre-wave 5G require powerful and efficient GaAs ICs that are housed in carefully chosen packages

#### news

- 06 MicroLEDs: a market of exponential growth

- 07 Transphorm and Microchip collaborate

- 08 AXT qualifies new GaAs line

- 09 Cree's latest 650 V MOSFETs offer efficiency to enable EVs, data centres and solar

- 10 Silicon laser now within reach

- 11 NREL six-junction cell sets efficiency records

- 12 Laytec tool plays key role in VCSEL research

## news analysis 14 A different kind of GaN

UK start-up, Porotech, is set to commercialise porous GaN, opening the door to highperformance optoelectronic devices with unexpected properties

## research review 58 Improving VCSEL design

Curved mirrors and a longer cavity combat overheating in green-emitting VCSELs

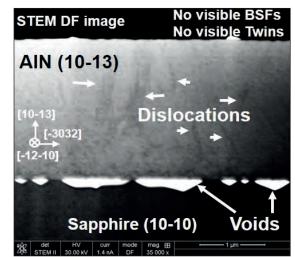

### 60 A better template for UV LEDs

UV emitters are set to benefit from high-quality, semi-polar templates formed by an ammonia-free growth process

#### 61 Epitaxial passivation aids novel FETs

Replacing the SiN passivation layer with thick, epitaxially grown AlGaN eliminates dispersion in polarisation-graded FETs

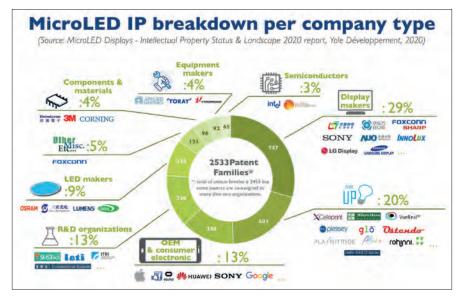

# MicroLEDs: a market of exponential growth

IN YOLE'S latest microLED display report, its analysts estimate that the cumulated effort in microLEDs to date reaches close to \$4.8 billion, with Apple alone close to \$1.8 billion, factoring in both the Luxvue acquisition and internal developments.

Excluding this acquisition and the recent deal between Facebook and Plessey, start-ups have raised a cumulated \$800 million to date and could add another \$100 million in 2020 pending disruption due to the Covid-19 pandemic. In addition, panel makers such as Samsung, LG, AUO and Innolux also significantly increased their efforts.

"The growth is fuelled by the meteoric rise of Chinese companies", asserts Eric Virey, principal display market and technologies analyst within the Photonics, Sensing & Display division at Yole Développement. "This mirrors a more general trend in the country as it transitions from a manufacturing to an innovation driven-economy. This also reflects the situation in the display industry where Chinese companies now hold more than 50 percent of the worldwide display capacity in 2020."

About 5,500 patents filed by more than 350 organisations and representing almost 2,500 families have been identified and selected by Yole. The level of activity is growing exponentially with 40 percent of the patents filed in 2019 alone.

"The increase in patents coming from China is remarkable", comments Virey. "Many of those microLED patents are questionable. Nevertheless, established players shouldn't underestimate their Chinese competitors and dismiss the threat: some patents show world-class innovation and demonstrate a strong resolve to close the gap with established rivals." In addition, in high volumes, even low-quality patents can be used as bargaining tools to fend off infringement lawsuits, negotiate cross licensing agreements and so on.

The proliferation of sub-par patents may however hinder innovation as it increases barriers to entry: increasing resources are required to conduct freedom-to-operate analysis, monitor patent activities, try to

invalidate wrongly granted patents and respond to infringement lawsuits.

Over the last two years, the industry has entered what can be seen either as a virtuous cycle or a bubble: companies are jumping on the microLED bandwagon for fear of being left out.

Virey explains: "Display makers dominated IP activity in 2019. Most were initially dismissive of microLEDs, but all are now accelerating their effort. BOE now leads in volume with close to 150 new patent families in 2019 alone."

LG, AUO, Samsung, CSOT, Tianma, Innolux, CEC Panda, Visionox and companies in the Foxconn group all dramatically increased activity as well.

Korean firms are investing massively in OLEDs but microLEDs could be a credible alternative for high-end TVs. Chinese makers are at least three years behind Korea in OLEDs, so microLEDs could be a more differentiating play. For companies such as AUO or Innolux that haven't invested in OLEDs, microLEDs could be critical for long-term survival and allow them to remain relevant in various highend market segments without requiring OLED-like multi-billion dollar capex.

Many companies now have portfolio addressing multiple technology nodes. Licensing and legal battles will likely arise if microLED displays enter volume manufacturing. Except in the field of microdisplays where the most capexintensive manufacturing steps can easily be outsourced, start-ups and small companies are not planning to become display makers. Rather, most will focus on their core expertise and attempt to license their technology to established display makers and OEMs.

In order to compete with LG's white OLED and maintain its leadership in the high TV market segment, Samsung Display Company announced a \$13 billion investment to develop and manufacture QD-OLEDs by 2021-2022. But Samsung is hedging its bets: its Visual Display group is developing microLEDs using in house mass transfer and chips developed by Playnitride.

Surprisingly, activity at Apple has slowed significantly since 2017. The few patents it has since published, however, show the high level of maturity and advancement reached by the company in microLED display technologies. Recent patents also show that the company has expanded the scope of its effort into developing microdisplays for augmented reality. Overall, the reduced activity could also be a sign of confidence in an already robust microLED portfolio as the company now focuses on setting up its supply chain. If successful, Apple would be the first to disrupt the industry by having developed its own display technology and establishing a mostly fabless supply chain model, something that Huawei could be willing to emulate.

news review

# Transphorm and Microchip collaborate

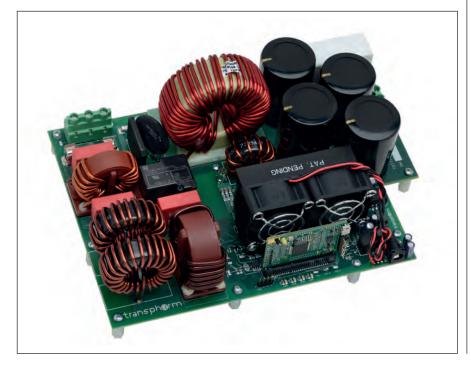

TRANSPHORM has announced that it has partnered with microcontroller provider Microchip Technology to integrate a Microchip dsPIC33CK digital signal controller board with Transphorm's 4 kW AC-to-DC bridgeless totem power factor correction (PFC) GaN evaluation board.

Building on Transphorm's application support capabilities, Microchip's worldwide technical support team will also be available to developers working with the integrated Transphorm solution.

As a result, customers can access an evaluation board offering more than 99 percent efficiency and preprogrammed firmware off the shelf, now backed with global support to further simplify AC-to-DC power system designs.

"Transphorm's Microchip collaboration is a gamechanger," said Philip Zuk, VP of Worldwide Technical Marketing and North American Sales, Transphorm. "The control requirements of GaN power systems using the bridgeless totem-pole power factor correction is different than what is used to control traditional CCM boost PFCs, which has long been a new challenge for some ODMs. Today, two industry leaders have partnered to reduce that knowledge gap. We're giving customers access to a disruptive GaN solution backed by a world-class global support team."

Microchip's dsPIC Digital Signal Controllers (DSCs) are supported by a set of embedded design tools created to empower developers, even those with limited expertise. These tools provide intuitive graphic user interfaces for device initialisation in Microchip's free MPLAB X Integrated Development Environment. The software tools are complemented by a full line of programmer, debugger and emulator accessories.

"Microchip's dsPIC DSCs are designed to meet the demanding control needs associated with newer digital power topologies," said Joe Thomsen, VP of MCU16, Microchip. "We are proud to work alongside a likeminded industry disruptor, Transphorm, to provide our customers this reference design including Transphorm's proven GaN devices. Our dsPIC33CK PIMs will offer engineers the flexibility and worldwide support that many designers need for their high-power solutions."

# RF GaAs Revenue Declines in 2019

REVENUE from RF GaAs-enabled devices fell by nearly 6 percent in 2019, marking the biggest decline since 2004. The Strategy Analytics Advanced Semiconductor Applications (ASA) report *RF GaAs Device Industry Forecast: 2018 - 2024* identifies declining smartphone shipments as the primary culprit for this drop in GaAs revenue.

The report does go on to forecast that growth will resume, allowing RF GaAs device revenue to approach \$9 billion by 2024. Drivers for this renewed growth will be the quickening pace of 5G network and device deployments.

"Wireless applications, particularly cellular terminals, dominate GaAs device revenue," noted Eric Higham director of the Advanced Semiconductor Applications (ASA) service. "Smartphones contain substantial GaAs content, so it was no surprise when declining shipments in 2019 pulled down the entire GaAs market."

He went on to say, "Despite the uncertain Covid-19 implications, I remain optimistic that expanding deployments of 5G devices and networks will become the new growth engine for GaAs device revenue. We will be monitoring developments at GaAs handset PA manufacturers like Skyworks, Qorvo and Broadcom to get better clarity about the 5G growth trajectory."

# AXT customer qualifies new GaAs line

AXT, a manufacturer of compound semiconductor substrates, has announced that one of its largest GaAs wafer substrate customers has formally qualified the company's new GaAs substrate processing facilities.

"Among the customers now qualified on the new GaAs manufacturing line, we are pleased to announce that one of our largest GaAs customers has qualified our new manufacturing sites for volume production," said Morris Young, chief

executive officer. "This Tier-1 customer has among the highest quality, safety and environmental standards in its industry. Its confirmation is an important milestone for AXT's manufacturing relocation, and will enable us to meaningfully ramp production from our new locations to meet our customers' needs over the coming quarters."

During the fourth quarter of 2019, AXT transferred its GaAs crystal growth ingot production to its new manufacturing facility in Kazuo, a city approximately 250 miles from Beijing. Wafer processing for GaAs was relocated to its new manufacturing facility in Dingxing, a city approximately 75 miles from Beijing. AXT began offering wafers from Dingxing for customer qualification in 2019, and began customer site qualifications later that year.

"Our new manufacturing sites are optimised for best-practice manufacturing techniques, and we have installed state-of-the-art equipment. Both are designed to meet and exceed the current

rigorous safety and environmental standards in China," Young continued.

"We now have capacity in place to meet today's demand for a wide variety of high-end applications, with ample space to expand as demand increases and new applications come to market. I am proud of the teamwork and dedication of our entire AXT team, making this significant accomplishment possible. We are now well positioned to push our technology to new levels of performance required by current emerging applications, and to engage the marketplace with confidence and enthusiasm."

AXT began manufacturing its GaAs substrate wafers in the Tongzhou district of Beijing, China in 2000. In 2015, the Beijing city government selected Tongzhou for its new municipal headquarters.

Along with many other businesses asked to relocate their manufacturing lines in order to create room and upgrade the district, AXT was instructed to relocate its GaAs manufacturing line.

# AquiSense launches UV-C LED surface disinfection system

AQUISENSE TECHNOLOGIES, a US-based maker of UV LED disinfection technology, has launched the PearlSurface 24G9, one of the first UV-C LED surface disinfection products designed for health care applications such as reuse of N95 face masks and other PPE.

The PearlSurface 24G9 offers advanced benefits specific to LEDs, including mercury-free lamps, instant-on operation and a low cost-of-ownership, while providing high-power density, homogeneous disinfection of target objects.

According to the company, the PearlSurface 24G9 offers simple operation, an integrated timer, a low voltage power supply and a compact footprint, making it suitable for point-of-use hospital settings, care homes, ambulances, police/fire departments, factories, food preparation, and so on.

AquiSense says it will offer this product under the current US FDA enforcement relief to deal with immediate Covid-19 emergency use and will simultaneously submit a pre-market approval application.

pearlsurf

"We accelerated our product development pipeline in response to immediate global needs for reliable reuse disinfection products," said Oliver Lawal, CEO at AquiSense Technologies.

"We are fortunate to be able to leverage an existing high-output UV-C LED module from our water treatment products and draw on our experience in rapid hardware design and optical modeling to ensure a high-level disinfection efficacy." concluded Lawal.

AquiSense Technologies is interested in talking to potential partners and distributors for the PearlSurface 24G9.

# Cree's latest 650 V MOSFETs offer efficiency to enable EVs, data centres and solar

CREE has announced the expansion of its product portfolio with the release of the Wolfspeed 650 V SiC MOSFETs, delivering a wider range of industrial applications and enabling the next generation of Electric Vehicle (EV) onboard charging, data centers, and other renewable systems with industryleading power efficiency.

"Cree is leading the global transition from silicon to silicon carbide, and our new 650 V MOSFET family is the next step in delivering a high-powered solution to a broader application base, including industrial applications everywhere," said Cengiz Balkas, senior vice president and general manager of Wolfspeed. "The 650 V MOSFETs deliver power efficiencies that help today's biggest technology leaders create the next generation of onboard EV charging, data centers, and energy storage solutions to reshape our cloud and renewable energy infrastructures."

The new 15 m $\Omega$  and 60 m $\Omega$  650 V devices, which use Cree's industry-leading, thirdgeneration C3M MOSFET technology, deliver up to 20 percent lower switching losses than competing SiC MOSFETs and provide the lowest on-state resistances for higher efficiency and power dense solutions. End users benefit from lower total cost of ownership in a variety of

applications through the more efficient use of power, reduced cooling requirements, and industry-leading reliability.

Compared to silicon, Wolfspeed's new 650 V SiC MOSFETs deliver 75 percent lower switching losses and a 50 percent decrease in conduction losses which results in a potential 300 percent increase in power density.

It is claimed that design engineers can now meet and exceed the industry's most ambitious efficiency standards, including 80 Plus Titanium requirements for server power.

The new 650 V MOSFET family is also said to be ideal for on-board chargers (OBCs) in the electric vehicle (EV)

market. The increased efficiencies and faster switching allow customers to design smaller solutions with added performance. Wolfspeed's 650 V SiC MOSFETs also enable bi-directionality in OBCs without compromising the size, weight and complexity of the solution. Furthermore, Wolfspeed's experience with automotive AEC-Q101 qualification, proven in the E-series MOSFET family, paves the way for future automotive qualified 650 V MOSFETs.

Other industrial applications, such as general-purpose switched mode power supplies (SMPS), will also be able to take advantage of the many benefits of the new 650 V SiC MOSFETs from the largest, global and vertically integrated supplier of SiC technologies.

## Advanced Compound Semiconductor **Foundry Services**

MOCVD • Fabrication • Testing

Advanced III-V semiconductor solutions for optoelectronics application in the biotechnology, telecommunications, energy, industrial, and defense industries.

MasimoSemiconductor.com | 603-595-8900

# Silicon laser now within reach

A TEAM from the Technical University of Eindhoven (TU/e) and the Technical University of Munich (TUM) has now succeeded in developing light-emitting, silicon-germanium alloys. As a result, the development of a silicon laser capable of integration into today's chips is within reach for the first time.

For the past half century, researchers have tried in vain to build silicon or germanium-based lasers. Silicon normally crystallises in a cubic crystal lattice. In this form it is not suitable for converting electrons into light.

Together with colleagues from the Technical University of Munich and the universities in Jena and Linz, researchers at the Technical University of Eindhoven have now developed alloys made of germanium and silicon capable of emitting light.

The crucial step was the ability to produce germanium and alloys from germanium and silicon with a hexagonal crystal lattice.

"This material has a direct band gap, and can therefore emit light itself," says Jonathan Finley, professor of Semiconductor Quantum Nanosystems at TUM.

Erik Bakkers and his team at TU Eindhoven first produced hexagonal silicon back in 2015. They started by growing a hexagonal crystal structure with nanowires made of another material. This served as a template for a germanium-silicon shell on which the underlying material imposed its hexagonal crystal structure.

Initially, these structures could not be stimulated to emit light. Through the exchange of ideas with colleagues at the Walter Schottky Institute at the Technical University of Munich, who analysed the optical characteristics with each successive generation, the production process was finally optimised to a grade of perfection where the nanowires were indeed capable of emitting light.

"In the meantime, we have achieved properties almost comparable to InP or GaAs," says Bakkers.

As a result, it appears to be just a matter of time before a laser made from germanium-silicon alloys and capable of integration into conventional production processes is developed.

"If we can implement on-chip and interchip electronic communications by optical means, speeds can be increased by a factor of up to a thousand," says Jonathan Finley.

"In addition, the direct combination of optics and electronics could drastically reduce the cost of chips for laser-based radar in self-driving cars, chemical sensors for medical diagnostics, and air and food quality measurements."

# microLED display developer to work with Facebook

PLESSEY, an embedded technologies developer of microLED technology for augmented and mixed reality (AR/MR) display applications, has announced a new venture.

Plessey will work with Facebook to help achieve their vision of the next computing platform centred around people. Under a new commercial agreement, LED manufacturing operations will be dedicated to helping Facebook prototype and develop new technologies for potential use in the AR/VR space.

With consumer devices like Oculus Quest and a continued legacy of breakthrough research, Facebook is one of the companies bestpositioned to make consumer-ready AR glasses a reality.

Plessey share that vision for a future where technology and the barriers between people disappear. Over the last two years, Plessey has been hard at work making the pivot from legacy semiconductor business into microLED's for AR displays, garnering numerous accolades and industry recognition.

Keith Strickland (Co-CEO/CTO) said "We are delighted to announce this new commercial agreement with Facebook. Plessey has been at the forefront of microLED display development and this agreement recognises the significant advances in our capabilities that we have made in recent years and we very much look forward to working with Facebook to help bring their vision to life."

# NREL six-junction cell sets efficiency records

SCIENTISTS at the US National Renewable Energy Laboratory (NREL) have fabricated a solar cell with an efficiency of nearly 50 percent.

The six-junction solar cell now holds the world record for the highest solar conversion efficiency at 47.1 percent, measured under concentrated illumination. A variation of the same cell also set the efficiency record under onesun illumination at 39.2 percent.

"This device really demonstrates the extraordinary potential of multi-junction solar cells," said John Geisz, a principal scientist in the High-Efficiency Crystalline Photovoltaics Group at NREL and lead author of a new paper on the recordsetting cell.

The paper, *Six-junction III-V solar cells with 47.1 percent conversion efficiency under 143 suns concentration* appears in the journal *Nature Energy*. Geisz's co-authors are NREL scientists Ryan France, Kevin Schulte, Myles Steiner, Andrew Norman, Harvey Guthrey, Matthew Young, Tao Song, and Thomas Moriarty.

Each of the cell's six junctions is designed to capture light from a specific part of the solar spectrum. The device contains about 140 total layers of various III-V materials to support the performance of these junctions, and yet is three times narrower than a human hair. Due to their highly efficient nature and the cost associated with making them, III-V solar cells are most often used to power satellites, which prize III-V's unmatched performance.

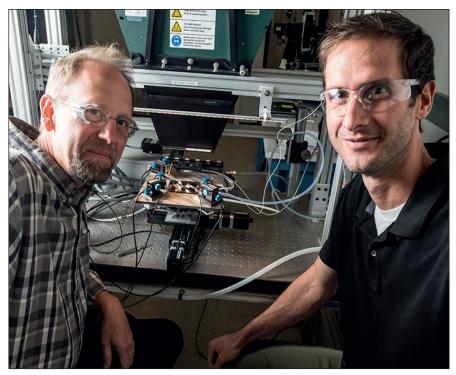

Scientists John Geisz (left) and Ryan France (right).

On Earth, however, the six-junction solar cell is well-suited for use in concentrator photovoltaics, said Ryan France, co-author and a scientist in the III-V Multijunctions Group at NREL.

"One way to reduce cost is to reduce the required area," he said, "and you can do that by using a mirror to capture the light and focus the light down to a point. Then you can get away with a hundredth or even a thousandth of the material, compared to a flat-plate silicon cell. You use a lot less semiconductor material by concentrating the light. An additional advantage is that the efficiency goes up as you concentrate the light."

France described the potential for the solar cell to exceed 50 percent efficiency as "actually very achievable".

Geisz said that currently the main research hurdle to topping 50 percent efficiency is to reduce the resistive barriers inside the cell that impede the flow of current. Meanwhile, he notes that NREL is also heavily engaged in reducing the cost of III-V solar cells, enabling new markets for these highly efficient devices.

news review

# Laytec tool plays key role in VCSEL research

LAST YEAR, scientists from Meijo University and the R&D division of Stanley Electric in Japan demonstrated high-efficiency and high-power operation for blue GaN-based VCSELs with AlInN / GaN distributed Bragg reflectors (DBRs). They published the results in *Applied Science*.

These AllnN /GaN DBRs are used at the front (emitting) side of the VCSEL that emits through the GaN substrate and is completed by a second, dielectric DBR at the VCSEL's backside. Hence, perfect lattice match of the AllnN in the front DBR is essential for enabling extremely lowdefect InGaN layers in the active zone of the device that is grown on top of the AllnN /GaN DBRs.

Now, the German metrology company Laytec has reported that a paper in the *Journal of Crystal Growth* by scientists from Meijo University shows the power of its EpiCurve TT metrology tool in revealing and controlling the AllnN strain and alloy compositions at accuracy levels of XRD already during growth of the epitaxial layers.

The team developed a model for

*in-situ* wafer curvature values of AllnN/GaN DBRs and determined InN mole fractions in the DBRs with the model.

In order to develop the model, they experimentally investigated contributions of substrate temperature ramping and a GaN growth to changes in the *in-situ* curvature values during the AlInN/GaN DBR growth.

They found that an increase of curvature changes at the substrate temperature ramping steps was explained by an increase of the total epitaxial layer thicknesses.

Another finding was that strain in the GaN layers at the GaN layer growth steps was almost zero.

Finally, they determined the InN mole fractions in the AlInN layers by using the model, showing excellent agreements with the values estimated from *ex-situ* X-ray diffraction measurements.

The model reveals not only the entire *in-situ* curvature change profile but also the InN mole fraction under the precisely lattice-matched condition of AlInN/GaN DBRs.

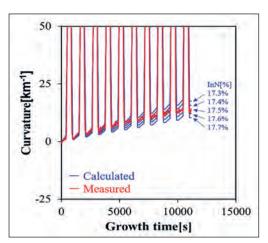

Fig. 1a: Measured *in-situ* wafer bow of GaN/AlInN DBRs on a GaN substrate as measured (red line) and simulated for several InN mole fractions (blue lines). Shown is a magnified view to the low-temperature (825°C) AlInN wafer curvature sequence.

InN mole fraction values estimated from the *in-situ* curvature measurements and the ex-situ XRD measurements.

The health and well-being of AngelTech speakers, partners, employees and the overall community is our top priority. Due to the growing concern around the coronavirus (COVID-19), and in alignment with the best practices laid out by the CDC, WHO and other relevant entities, AngelTech decided to postpone the live event to the 17 - 18 November.

In the interim, we believe it is still important to connect the community and we want to do this via an online summit, taking place live on Tuesday 19 May and content available for 12 months on demand. This will not replace the live event (we believe live face to face interaction, learning and networking can never be fully replaced by a virtual summit), it will supplement the event, add value for key players and bring the community together digitally.

The event will involve 4 breakout sessions for: CS International **PIC Pilot Lines**

### Key elements of the online summit:

- Covering key topics of the industries

- Live 3 hour online summit

- 10 minute presentations learn from experts in the industry

- Recorded product demos

- Live audience questions

- Enhanced discussion and audience interaction

- Video panel sessions

- Sponsors digital booth (intro video,

# Tuesday 19 May 2020

- company content, lead generator, facilitate one on one video meetings with attendees)

- Live private video meetings between two or more attendees

- After the live event, monthly keynotes to drive traffic to the event 24/7, 365

#### www.onlinesummit.angel-tech.net

Innovation is in AngelTech's DNA and we are leveraging this strength to bring you an immersive and inspiring online event without the risk of travel during this uncertain period.

$\times$ info@angel-tech.net

We have opened the online summit to the whole industry. In a time of great uncertainty and where live face-to-face conferences are suspended, we want to do our bit to keep key players connected in the industry and continue from strength to strength

+44 (0) 2476 718970

# **REGISTER TO ATTEND FOR FREE: onlinesummit.angel-tech.net/#register BECOME AN EVENT PARTNER: onlinesummit.angel-tech.net/#partners**

# A different kind of GaN

UK start-up, Porotech, is set to commercialise porous GaN, opening the door to high-performance optoelectronic devices with unexpected properties, reports Rebecca Pool.

> A RELATIVELY UNKNOWN MATERIAL from a newly minted UK start-up is set to make waves in the rapidly growing GaN market.

> With a host of novel properties that open the door to high-performance optoelectronic devices, 'porous GaN' is attracting more and more interest in compound semiconductor circles. And thanks to  $\pounds 1.5$  million in investment funds, University of Cambridge spin-off, Poro Technologies – or Porotech – is on course to be one of the first companies to bring this mesoporous version of GaN to market.

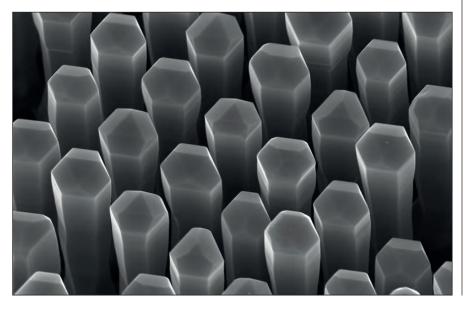

Seed round investment is being used to develop a pilot plant in Cambridge, UK, and Porotech's first products. Porous GaN can be regarded as a semiconductor composite of solid GaN and air. As Rachel Oliver, Cofounder and Chief Scientific Officer of Porotech, and Director of the Cambridge Centre for Gallium Nitride puts it: "Porous GaN is basically GaN with holes in it that are a few tens of nanometres across."

"With porous GaN we can engineer a wide range of material properties... and offer a new material platform to build semiconductor devices on," she adds.

The Porotech team creates the nanoscale porosity in GaN wafers using electrochemical etching. The etch is conductivity selective and responds differently to the material depending on its doping density. Porosity is created in doped layers while undoped layers are left undamaged, allowing complex three-dimensional nanostructures to be created.

According to Oliver, the etchant flows to and from the doped layers via the many nanometre-scale channel-like defects – dislocations – that exist within any GaN wafer.

"Even your best quality GaN wafer will still have around 10<sup>5</sup> dislocations per square centimetre," she explains. "So the etchant will flow down a dislocation and when it hits the doped layer will etch it very quickly to create the porosity before continuing down that channel to the next doped layer."

"We can take an entire wafer, and using this conductivity selective etching mechanism, create GaN [structures] with a whole new set of properties that haven't been available before," she adds. "It's very cool from a commercial perspective."

Indeed, both Oliver and Porotech chief executive and co-founder Tongtong Zhu are certain their porous GaN fabrication process lends itself to commercial exploitation. The method has been tried and tested for wafers up to eight inches in diameter and Zhu reckons it will seamlessly scale to even larger wafer sizes.

## news analysis

"The first thing that inspired us to pursue this process commercially is that it works with wafers," says Zhu. "What's more, during the process we preserve the surface quality and the integrity of the materials so anyone can take the porous GaN wafer and insert it into their production processes without any disruption."

#### Devices to go

Oliver, Zhu and colleagues have already fabricated several components and device prototypes. They have demonstrated highly reflective Distributed Bragg Reflectors (DBRs) – or 'Poro Mirrors' – based on wafers comprising alternating layers of solid and nanoporous GaN. InGaN LEDs were then grown on these epi-ready DBR pseudo-substrates that were some 25 percent more energy efficient than standard LEDs.

"This DBR substrate is fully compatible with GaN so a customer doesn't need to process anything differently during LED fabrication, but can still get a brighter and more efficient LED," points out Zhu.

Porotech has also joined forces with other institutions and start-ups to fabricate thermal sensors that use porous GaN layers as on-chip thermal insulation. And in a novel technology twist, the team has filled the pores in a porous GaN wafer with a halide perovskite to create an optoelectronic material with longer-lasting luminescence.

"These luminescent perovskites are useful in solar cells and LEDs but degrade very quickly," says Oliver. "We can slow this degradation down with porous GaN."

Excitingly, novel porous GaN devices could be reaching commercial markets sooner rather than later. Despite the coronavirus pandemic, the Porotech pilot plant is NID-GaN m-GaN m-GaN m-GaN MID-GaN NID-GaN MID-GaN NID-GaN NID-GaN NID-GaN NID-GaN NID-GaN NID-GaN

currently being built at Cambridge, and Oliver, Zhu and colleagues are transferring production process from the laboratory to the plant.

"The plant will be operational before June this year and we're going to start with small-scale production to show that our wafers can be produced in volume," says Zhu. "We're currently preparing tens of wafers for customer trials and eventually intend to demonstrate that we can produce thousands of wafers a year."

The company is also working with foundry services, wafer producers and integrated device manufacturers, and hopes to license out technology in the coming years. "We've been working to get the company off the ground for several years and we aren't going to stop now," says Oliver. "There has been no other time when GaN is rising so quickly and we have to keep up our momentum."

Poro Technologies co-founders (left to right): Tongtong Zhu (CEO), Rachel Oliver (CSO), Yingjun Liu (CTO)

MAY 2020 | WWW

**VRIGHT COMPOUND**

MICONDUCTO

Electrochemical etching provides nanoscale porosity

# A knowledgeable, responsive partner for plasma technologies

Shipments of Oxford Instruments Plasma Technology's deposition and etch tools are rising, due to their deployment in critical processes used for chip manufacture in growing markets

### BY RICHARD STEVENSON

HAS THERE EVER BEEN a better time to be working within the compound semiconductor industry? Never before have there been so many emerging markets tipped to generate billions and billions of dollars in device sales. Over the next few years shipments of GaN transistors will underpin the roll-out of 5G infrastructure; SiC transistors and diodes will enhance electric vehicles; GaAs VCSELs will become more common in smartphones and provide a source for other 3D sensing applications; and interest will mushroom in photonic integrated circuits, which can be used for communication and sensing.

All this activity is particularly good news for the makers of processing equipment for the compound semiconductor industry. That includes Oxford Instruments Plasma Technology, a division of Oxford Instruments based in Yatton, just outside Bristol.

According to Managing Director of Plasma Technology, Mike Gansser-Potts, the compound semiconductor market is now entering a high-volume manufacturing phase where the performance it enables is demanded by global trends, such as efficient energy and driverless vehicles.

Plasma Technology is in a particularly strong position to make the most of these opportunities, because it has been supporting its customers on the research and development of these devices for almost forty years.

"We have already had success with customers, VCSEL manufacturers for example, transitioning from corporate R&D into high-volume manufacturing," says Gansser-Potts. "We achieve this by truly understanding the customer's devices and how our systems can enhance the performance of these devices."

The strategy of Plasma Technology is to focus on critical layers and steps within the device process flow, where it has a deep understanding and can bring value. It can increase device performance, while bringing down the cost of the wafers, says Gansser-Potts. "We have major investment across the company to achieve this."

Some of the companies that Gansser-Potts and his colleagues are working with are device makers that are in the late research stage, or in the corporate research stage. For these firms, Plasma Technology is accompanying them on their journey to production. When they succeed, Plasma Technology's tools are qualified before the chipmaker enters high-volume production.

Working with a client in this manner is beneficial on two fronts says Vice-President of Strategic Production Markets, Brian Dlugosch. He points out that it brings in revenue from the outset, and it leads to sales during the manufacturing phase. "That allows you to make money with your equipment for a longer period of time."

Plasma Technology is also well-positioned to assist in the R&D sector, where the company has held a strong position for decades. Today it is showing no signs of complacency, having recently appointed a market specialist to oversee its activities in that area. Staff are

## cover story plasma processing

also being recruited to support the production side of the business, where there has been the launch of new software and hardware.

"We have just launched Atomfab, for example, which is much faster than any product we have produced before for atomic layer deposition," says Gansser-Potts. "And we are just launching PTIQ, which is our control software that is much more tailored to a production environment."

With so many market opportunities available right now, it is critical to direct efforts at the ones offering the best chances of success. "If we try and spread the net too wide, we will have a small amount of many different markets," reasons Gansser-Potts, who has adopted and led a well-defined strategy: focusing on really critical processes where Plasma Technology has a competitive advantage and a relationship with the developing client base.

#### A plasma portfolio

By offering a portfolio of tools, the engineers at Plasma Technology can help customers to find the

> most suitable one for their needs. For example, if device makers need to etch AlGaN, they can choose between equipment that provides an inductively coupled plasma etch and that producing an atomic layer etch.

In addition, customers may choose to buy several tools, each carrying out a different step in the production process. One obvious benefit is that the fab has to deal with fewer tool suppliers. But that's not the only gain – it also allows the use of a cluster system, which can improve the quality of the interface between the oxide and the semiconductor, by avoiding vacuum breaks between process steps.

> Rewind the clock a few years and many customers would buy tools, shut the door and rarely communicate with their supplier. Today, however, that's not the norm – many chipmakers now want assistance and support. "We see customers that are in corporate R&D that are willing to pay big service contracts, saying yes we want maintenance, yes we want spare parts," explains Mark Dineen, Technical Marketing Manager at Plasma Technology.

It's a change that reflects the gradual shifting of the compound semiconductor industry towards the working practices of the more mature, more open silicon industry. There, market strength is reached by helping customers to increase the number of good wafers produced each day, while lowering the cost. The chipmakers in the silicon industry are not concerned by the appearance of the tool. Klaas Wisniewski, Strategic Business Development Director, hopes that the compound semiconductor industry moves in the same direction, placing value on how Plasma Technology can help to lower cost, increase throughput and enable device functionality.

Efforts on all these fronts are supported by the work in the Application Lab. In the last decade, the company has made much investment in this, installing 25 process chambers at their main facility, and another seven at a facility in Taiwan. Using

Atomfab is a newly released product that sets a new benchmark for plasma-enhanced, atomic-layer deposition.

## cover story plasma processing

these chambers, Plasma Technology's engineers undertake marathon runs and see if there are any changes to process or material characteristics. This allows the company's technical team to advise on when it is necessary to clean a tool, and how far a particular parameter can shift before it changes the material properties. Assessments are made with a suite of characterisation techniques that include ellipsometry, atomic force microscopy, scanning electron microscopy and confocal microscopy. A Raman spectrometer is being installed. To obtain device results, Plasma Technology collaborates with companies and universities.

#### Supporting customers

If firms that have invested in Plasma Technology's tools run in to problems, engineers can pay a visit and help find a solution. When an emergency occurs, responses are quick wherever the customer may be, thanks to qualified engineers located at seven sites – one is in China, another in Japan, and there are also those in the US, Germany, Singapore, Taiwan and the UK. However, these days, thanks to remote access of data from tools, often all that's needed is a 'phone call.

Oxford Instruments hasdeveloped new processing solutions in its fully equipped lab in Yatton, UK.

"We have seen a huge growth in remote access to our equipment, so there is less need for hands-on," explains Dean Furlong, Engineering and Global Services Director. "Two years ago we had pretty much zero remote access. We are now doing thousands and thousands of hours every month of remote support with our customers, whether that is advice, support or improvements."

This is a significant change, as in years gone by, most chipmakers would have never shared any of their data with equipment manufacturers.

"We are trusted, and trusted significantly, but I don't think it's about us," says Furlong. "It's about a change in understanding the way the technology works." A protected environment provides data transmission up to the cloud. For some device manufacturers, a willingness to share data also reflects a narrowing of their view in what is proprietary.

While some customers will welcome a closer relationship with a toolmaker, there are others that prefer to get on by themselves – at least, until there is a problem they can't fix! For firms with that philosophy, Plasma Technology offers self-sufficiency packages. Once the chipmaker has bought the tool, its engineers are trained and certified on that equipment, so that they can manage themselves and utilise the software. However, if problems arise that they are unable to address, they can access immediate support by phone, and if necessary, have a visit from a Plasma Technology engineer, all as part of the package agreement.

For many years, Plasma Technology has offered tools for inductively coupled etching. Very recently, they have been complemented with equipment that can remove material by one atomic layer at a time. Together, these two etching techniques are ideal for the production of normally off AlGaN HEMTs, which have very thin layers, and a two-dimensional electron gas that must not be damaged

There are an increasing number of products to help customers in the fabs with diagnostics and support assistance. "We have something called LiveAssist, which enables us to have real-time connectivity to site, giving augmented reality support," says Furlong. Another improvement is the launch of the latest version of the company's software platform. "Within that there are modules on the roadmap for analytics and diagnostic suites, which will give further enhanced capabilities, not just for ourselves, but for our customers, in terms of understanding what is happening in their environment, and being able to do predictive analytics in tool behaviour."

"That predictive software is important because people don't want to operate in a run-to-fail mode," says Dlugosch. Instead of using a component to the end of its lifetime, engineers are now changing it at an earlier stage so that they can maintain production.

#### Deposition developments

At the SemiCon West exhibition last July, Plasma Technology added to its portfolio of atomic scale processing systems with the launch of AtomFab. It provides atomic layer deposition, and is designed to cater for the needs of makers of GaN power and RF devices.

"It really builds on our expertise on controlling the interfaces and ensuring that plasma processing is low damage, but also delivers high-quality and high throughput," says Aileen O'Mahony, Product Manager, Atomic Scale Etching.

Dineen says that the introduction of AtomFab has gone extremely well, including the process transfer from the R&D platform to the high-volume manufacturing platform. "We maintained process performance at the device level while reducing the manufacturing cost per wafer for this process step by 75 percent." The company secured its first highvolume manufacturing production order five months after the product launch.

There have also been successful customer demonstrations provided at Plasma Technology's

site, and interest from chipmakers working with other devices that have concerns related to plasma and substrate damage.

During the development of the AtomFab, engineers at Plasma Technology engaged with customers that would consider using this tool for development or production, in order to understand their priorities. "That's really key, because we need to understand what they are working towards, because that will define the features," says O'Mahony. The team also wanted to discover what features the customer didn't value, to avoid including unnecessary capabilities. While some device manufacturers will be keen to buy a new tool, others will want to upgrade what they already have. That's possible, as detection systems and new software can be added to existing equipment to enhance its capabilities. However, some tools are now well off the pace - they can date back as far as the early 1980s - and if that's the case, it's more prudent to invest in state-of-the-art equipment.

#### **Enhanced etching**

For many years, Plasma Technology has offered tools for inductively coupled etching. Very recently, they have been complemented with equipment that can remove material by one atomic layer at a time. Together, these two etching techniques are ideal for the production of normally off AlGaN HEMTs, which have very thin layers, and a two-dimensional electron gas that must not be damaged. Inductively coupled etching can remove most material in good time, before atomic layer etching carefully takes away the last few atomic layers with great accuracy.

As the compound semiconductor industry has evolved, a growing number of device makers are having more stringent requirements related to the geometry of the processed wafer and the yield. This reflects the greater complexity of the design of many of today's devices.

"If you take a HB LED, you can get away with a lot more, because it's a larger area," says Rob Gunn, Senior Product Manager. With a microLED, the sidewalls have a far greater influence over device

## cover story plasma processing

A new software control solution delivers enhanced experience in a production environment. performance, so there is more concern related to their quality. Having worked with microLED pioneers from their development days, Plasma Technology is well placed to have tools and processes for high-volume production of these devices.

#### Global goals

Given the capability of Plasma Technology's tools to process SiC and GaN materials, it's of no surprise that it is keen to have a strong presence in the Japanese market, where there is the likes of Fujitsu, Sumitomo, Sony and Nichia. But winning sales is far from easy. "The Japanese market is very, very demanding, and it's culturally probably very challenging for the Western World," says Wisniewski. So to try and get around these obstacles, Plasma Technology is working with a Japanese process partner, Ulvac. "We have a commercial agreement with them to help us commercialise our technology in the Japanese market."

China may be best known for its highly competitive LED manufacture that has led to the commoditisation of this device. However, it is also active in other sectors of the compound semiconductor industry, where there are more promising opportunities for Plasma Technology. Right now, the Chinese government is working on the draft of its next five-year plan, which includes the classification of compound semiconductor materials under the third generation of semiconductors. "So it's big exposure into SiC, where we have qualified processes," say Wisniewski, who can also see a growth in activity in GaN RF, GaAs optoelectronics and microLEDs – all areas where Plasma Technology has great strength in critical processes.

For makers of these devices in China and beyond, Plasma Technology is a valued partner. For almost forty years it's been looking after its customers by developing and refining hardware and associated critical processes – fulfilling their wishes is in its DNA.

SUBMIT YOUR LAB& FAB ARTICLE

Research is the foundation for the growth of the compound semiconductor industry.

If you want to highlight the important breakthroughs that you make, submit your latest research stories to: Richard.Stevenson@angelbc.com

It is imperative that *Compound Semiconductor* remains a timely resource for this industry, so we are only interested in highlighting very recent work reported in academic papers.

Therefore, please only consider writing a short piece highlighting your work if you have a journal paper that has been accepted and about to appear in press, or a paper that has been published within the last month.

# The most cost effective method to excellent quality.

"Now offering Germanium Reclaim"

#### **III/V-Reclaim**

Wald 10 84568 Pleiskirchen / Germany Telefon: +(49) 8728-911093 Telefax: +(49) 8728-911156 E-Mail: sales@35reclaim.com Internet: www.35reclaim.com

- We recycle your GaAs and InP wafer (all formats and sizes)

- One and double side polished wafer

- Best surface quality for direct use in Epitaxy

- Backside thinning of fully structured wafer

- $\bigcirc$  Thin wafer (60  $\mu$ m)

- Single wafer processing possible

- We buy used wafer and sell recycled wafer

WORKING FROM HOME? NO PROBLEM

Our new web site makes access to information about our company, products and career opportunities easier than ever. Whether you are working at home or in the office, our easy to use desktop and mobile versions make it simple and quick to find what you want wherever you are. Why not fill in our contact form now to pre-order your copy of the new LAYERS 5 magazine coming out in April. www.evatecnet.com/about-us/contact-us/

ADVANCED PACKAGING • SEMICONDUCTOR • OPTOELECTRONICS • PHOTONICS • THE THIN FILM POWERHOUSE www.evatecnet.com

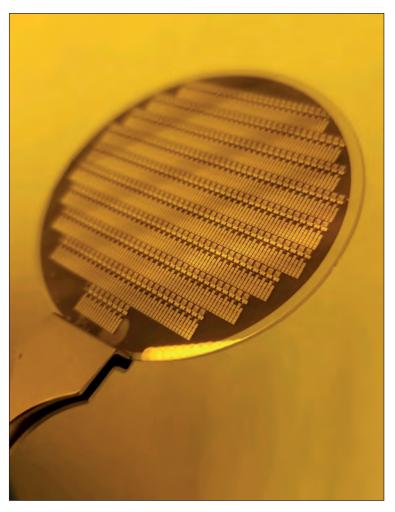

# AFRL: Breaking records with gallium oxide

Engineers at the US Air Force Research Laboratory are propelling the performance of gallium oxide devices to new highs, by realising record-breaking critical field strengths and making the first FETs with switching losses below those for silicon

### BY RICHARD STEVENSON

IF YOU HAVE to begin from scratch, it's very hard to develop a device with a new material. Efforts may have to begin by learning how to grow the crystals that are large enough to be sliced into native substrates. Much research may also be needed to work out how to deposit epilayers, make devices, test them, and then refine the processes. All this requires funding and a team of researchers with the right expertise to define an application space. Given all these challenges, it's no surprise that progress on making devices with a new material is far from immediate, with some groups only entering the field when they can draw on the success of others.

That's certainly the case with gallium oxide. Its attractive credentials have been known for many years – it is a material with an incredibly wide bandgap that indicates that it should make devices that are great for power switching – but it is only in the last decade that impressive device results have started to emerge from a few groups.

Laying the foundations for all the recent progress are materials scientists in Japan and Germany that developed processes to grow gallium oxide crystals from the melt and deposit epitaxial layers onto this foundation. The first application for gallium oxide was its use as a transparent conductive oxide substrate for GaN LED applications. But then researchers in Japan also made another important breakthrough – in 2012, a team at NICT, Japan, published experimental results showing a high breakdown voltage in gallium oxide devices made from the  $\beta$ -phase of the material.

One group that has noted NICT's success and gone on to break records by partnering with some material suppliers is a team from the Air Force Research Laboratory (AFRL) at the Wright-Patterson Air Force Base in Ohio. Viewing gallium oxide as a very promising candidate for fast, low-loss power switching, they have attracted much attention by: setting a new benchmark for the critical field strength of gallium oxide FETs; fabricating the first enhancement-mode gallium oxide MOSFET that delivers a high-voltage operation in the off-state; and producing the first gallium oxide FETs with RF gain and a power switching loss below that for silicon.

#### In the loop

In the early stages, the team at Ohio were led by AFRL Fellow Gregg Jessen. Initially, he directed his team to explore the new material via *ab-initio* first principles modelling. Results revealed that the velocity and high critical field strength have disruptive potential in fast power switching and RF power applications. Spurred on by these results, Jessen went to build a US gallium

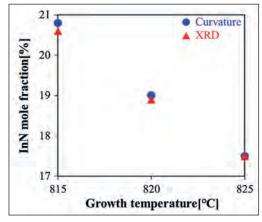

2-inch Synoptics gallium oxide substrate with an gallium oxide epitaxial layer and transistor fabrication completed by AFRL engineers.

[mn] Y

oxide research base and forge international partners, in order to gain access to some of the first devicequality samples.

"Gregg inspired not just our team, but the entire nation," credits Kelson Chabak, now the team leader at AFRL for device research after Jessen accepted a position in industry.

Chabak drew inspiration not only from device results obtained with NICT's MOSFET, but also: the availability of substrates, which can be produced from the melt; the opportunity for homoepitaxial growth with the  $\beta$ -phase of the material, leading to epitaxial films with a low defect density; and the simplicity associated with device fabrication. When the team fabricated their first device samples in 2015, Chabak wondered whether he and his co-workers could replicate the success of NICT and measure the purported high critical field strength.

Despite his curiosity, Chabak did not intend to change direction and switch from working on GaN to gallium oxide: "We weren't too invested in [gallium oxide] at the time. In fact, we were ready to pass on it if our early assessment of devices were to fail."

To evaluate the potential of this ultra-wide bandgap material, Chabak and his colleagues leaned on their international partners for epistructures. Although they had access to MBE tools at AFRL, they were primarily configured for fundamental research in GaN (Chabak and colleagues have tremendous expertise in this area, following two decades of work providing rapid feedback to the GaN material community).

Choosing to source gallium oxide epistructures initially actually had its benefits. It avoided having to procure expensive equipment and quickly gain epitaxial expertise in a new material. The team were also able

to form valuable international materials partnerships LatticeTemperature [K] ure (K) 396.0 376.0 628.0 356.0 545.0 462.0 336.0 316.0 379.0 Y [um] 296.0 Ga<sub>2</sub>O<sub>3</sub> MOSFET without a thermal solution Ga<sub>2</sub>O<sub>3</sub> MOSFET with flip-chip topside solution ~200 K/W -22 K/W ŵ X [um] X [um]

Technology computer-aided design simulation of thermal effects without and with a top-side solution implementing flip-chip technology, thick metal contacts, a thermally conductive passivation dielectric on the channel and aggressive lateral scaling in a gallium oxide device.

The researchers at AFRL have provided several significant contributions to the advance of gallium oxide devices.

to quickly move ahead on gallium oxide device research.

#### Sourcing material

Substrates came from Tamura, the only commercial supplier. This firm, which has worked closely with NICT, uses the edge-defined, film-fed growth process to produce material that is up to 4-inch in diameter in some orientations. Substrate dimensions for one of the most common orientations were initially 10 mm by 15 mm, but in the last year Tamura has also started to offer variants that are 25 mm by 25 mm. There is no observed degradation in quality with the larger sizes, according to Chabak, while price per unit area has fallen by around 50 percent.

The team at AFRL purchased these substrates and contacted Tamura's spin-off, Novel Crystal, to purchase epiwafers. In addition, the AFRL relied on another source of epitaxial growth, the Leibniz Institute for Crystal Growth, a facility more commonly known by the initials IKZ.

In 2015, IKZ provided the first samples to the US team. Success followed, helping this German institute to become a valued research partner with AFRL. It is a relationship that has blossomed, with both sides actively engaging in collaborative research.

By shipping high-quality material in good time, IKZ played a critical role in AFRL's success. "We were able to become leaders in our field because we secured early access to materials," admits Chabak.

The first milestone for this collaboration came in 2016, when AFRL device team member Andy Green fabricated and reported a MOSFET made from an IKZ epiwafer that blocked 230 V over a 0.6  $\mu$ m gatedrain drift region. That translates to a record-breaking average critical field strength of 3.8 MV/cm. To put this figure in perspective, most lateral GaN devices, after a few decades of research, operate at 1 MV/cm. "So

without much optimisation, we got about four times the critical field strength of GaN," enthuses Chabak. "That was the spark that started the fire."

Green's record-breaking result came from an epiwafer made by MOCVD at IKZ, with growth on an off-cut substrate to optimise the diffusion length of the adatoms. Note, however, that Chabak and his colleagues have also obtained good results on MBEgrown material, provided by Novel Crystal, so they are yet to decide on what growth technique is better for gallium oxide homoepitaxy. "The jury is still out, we've made good devices on both, and we are still assessing materials."

#### Side-stepping *p*-type problems

Later that year, the team from AFRL reported the first ever enhancement-mode FET with a high-voltage operation in the off-state. This ground-breaking result is important, as it shows that it is possible to fabricate a normally-off FET, despite the lack of *p*-type carriers in gallium oxide. Normally-off operation is highly valued, as it creates a device that is fail-safe, and can be driven with a unipolar power supply.

The key to this success is to employ the work function of the gate to pinch-off an array of non-planar fin channels. "We were the first ones to implement this with gallium oxide, but very similar things have been done with GaN," says Chabak.

Note that it would have been folly for Chabak and his co-workers to try and attack problems associated with *p*-type doping in gallium oxide head on. Holes are self-trapped, so they fail to contribute to carrier transport, and the flatness in the valence band results in a very heavy hole mass.

While *p*-doping is incredibly challenging, creating an abundance on unbound electrons in gallium oxide is relatively easy. There are three common dopants: silicon, tin and germanium.

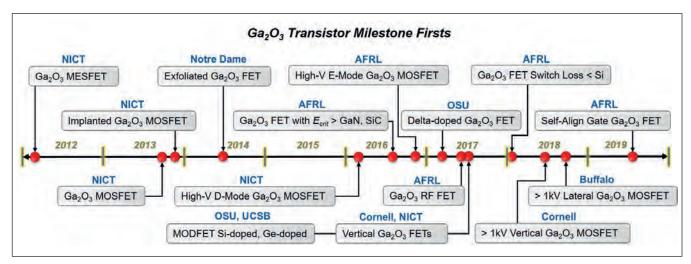

Veeco GenXcel oxide MBE tool located at AFRL dedicated to fundamental oxide materials and device research on up to 4-inch substrate sizes.

"All three of these dopants work, and we have made devices with them," says Chabak. According to him, merits of silicon include its familiarity – it is widely used to dope GaN and GaAs – and the ease with which it can be introduced successfully within a growth chamber. To realise high concentrations, delta-doping and contact re-growth is possible, which produces good results.

Implantation is another option for producing n-type material. Chabak views this as a tool that offers device engineering and lateral doping profiles, and allows the fabrication of transistors with self-aligned contacts – features that are difficult to implement in GaN.

Compared to wide bandgap materials, the temperature required to activate carriers in gallium oxide is quite low – in some circumstances, just 850 °C will suffice. Studies of this doping technique have led to some interesting results, such as finding that impurities diffuse along implanted, damaged regions.

#### Better than silicon

Chabak's team claimed their third record-breaking result in 2018, when they reported the first gallium oxide FET with a switching loss below that for silicon. "There were a few different design tricks that were implemented," reveals Chabak. Modifications included partially removing the channel to make it normally off, adding a gate-connected field plate to reduce the peak electric field and optimising device dimensions. Resistance fell by reducing the source-todrain distance, a feat realised without sacrificing the breakdown voltage.

Efforts at AFRL have also included an investigation of the RF characteristics of gallium oxide transistors. "We are very careful to say that we do not see gallium oxide replacing gallium nitride for RF devices," warns Chabak. "Gallium nitride devices will always be the king of RF power." However, he thinks that gallium oxide could become a complementary technology, as transistors made from this material may have the potential to provide a high efficiency, or deliver a higher output power, when configured in a particular class of operation.

The team has investigated the RF characteristics of devices with a 0.7  $\mu$ m gate length and a gate-recess, which reduces the channel thickness from 180 nm to around half that value. Small-signal measurements, using a drain-source voltage of 40 V, revealed a cut-

off frequency and maximum oscillation frequency of 3 GHz and 13 GHz, respectively. Driven in class A mode, output power is 0.23 W mm<sup>-1</sup> and the power added efficiency is 6.3 percent, according to CW large-signal power measurements at 800 MHz.

Severe heating limited the performance of these RF devices. That's also the case for most power devices made from gallium oxide, as both types of device are impaired by the low thermal conductivity of this material. Some critics claim that this is a severe impediment for the progress of this class of device, but Chabak disagrees, arguing that it is not a "showstopper". When discussing this issue with the naysayers, he is quick to point out that the thermal conductivity of GaAs, which is a mainstream RF power technology, is within an order of magnitude of that of gallium oxide.

To ensure that gallium oxide devices fulfil their potential, efforts will have to be directed at extracting heat from both the backside of the device, and the top, where the biggest gains can be made. "We have some preliminary modelling that suggests flip-chip technology can, when combined with backside waferthinning, reduce the overall thermal resistance of our devices to close to SiC."

Realising such success will not be easy, admits Chabak. "I don't expect it to be something that is solved in the near term." In fact, if significant progress is to be made, it will probably require the funding of major programmes. However, the approaches to explore this can draw on previous successes in the compound semiconductor industry. "Luckily we already have a lot of thermal management solutions, developed for gallium nitride and gallium arsenide. So we hope to take advantage of these."

Chabak and his co-workers are not planning to tackle this problem just yet. Instead, they will direct their short-term efforts at introducing electron-beam lithography to the fabrication process, and scaling transistors to below a micron. The devices that result could be very attractive candidates for fast-switching applications, by combining very high speeds with high breakdown voltages.

The team mainly collaborates with their gallium oxide materials partners for epiwafers. But that should

soon change, as last year the group invested in a state-of-the-art oxide MBE tool that can handle 4-inch substrates and produce gallium oxide epiwafers featuring either silicon or germanium doping. This reactor will also be used to produce heterostructures such as those containing aluminium gallium oxide.

#### Home-grown support

The introduction of the tool has expanded the number of researchers at the AFRL that are devoting at least some of their time to gallium oxide. A few years ago, efforts involved a smaller group of device engineers, all in the sensors group – but with the MBE machine on site and an exponential boom in interest, they now have participants from materials, devices and power groups across AFRL. "When we have meetings for gallium oxide, we can easily fill a large room now," says Chabak.

Once epiwafer production is in-house, the team will only need to source substrates. In the near-term they will continue to come from Tamura, but further ahead, they could be obtained from a domestic source. That's because AFRL has been funding a gallium oxide crystal growth programme at Synoptics, a subsidiary of Northrop Grumman.

"They are well ahead of the curve, because they have made crystals for lasers for a long time," says Chabak. Using the Czochralski technique, Synoptics has been able to grow, fabricate and polish semi-insulating (010) substrates up to 2-inches in diameter.

In the last few months, the team at AFRL have started to make devices using these substrates. "Are they comparable to Tamura? Some are – we're getting there," says Chabak.

In addition to this funding, AFRL recently initiated a program with Saint Gobain for edge-fed film growth of semi-insulating, (010) 2-inch gallium oxide substrates.

Creating domestic sources for large area gallium oxide substrates will be the missing piece for Chabak and his device team. In turn, this should lead to enhanced research and development, giving the team from the AFRL a good chance to add to their tally of record-breaking results for gallium oxide devices.

To ensure that gallium oxide devices fulfil their potential, efforts will have to be directed at extracting heat from both the backside of the device, and the top, where the biggest gains can be made

# Slashing substrate costs for CPV

Switching to a silicon foundation and re-using germanium substrates offer two options for driving down the cost of multi-junction cells

## BY RICHARD STEVENSON

THROUGH NO FAULT of its own, CPV may appear to have missed the boat. Many leading firms developing this technology have been killed off by a double whammy - a credit crunch that chocked further investment, and plummeting prices for silicon PV that blunted the competitive edge of this class of photovoltaics.

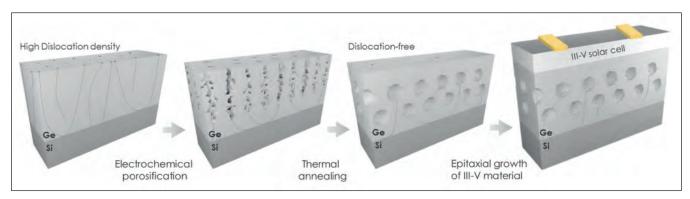

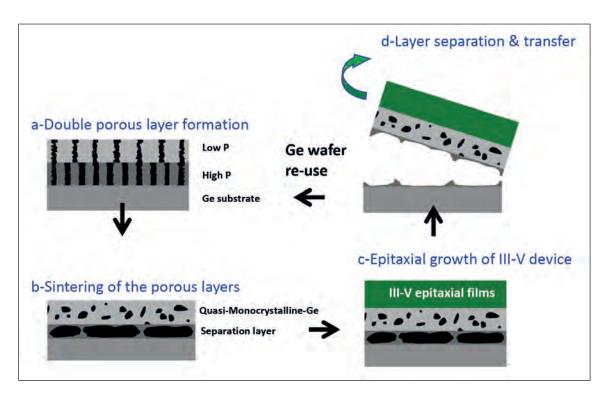

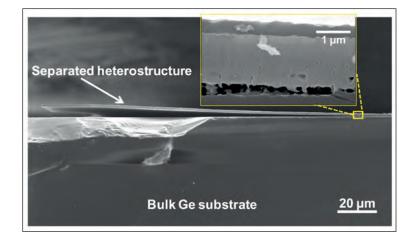

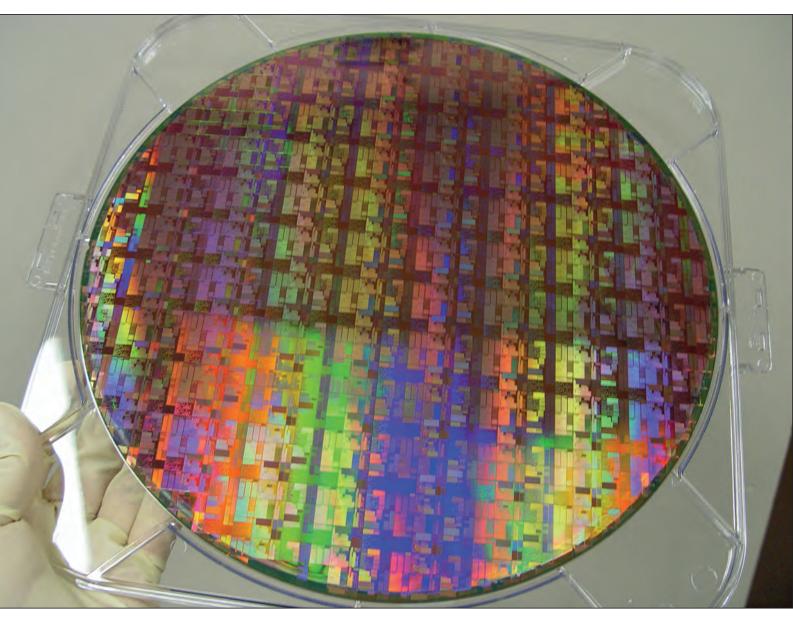

Given this state of affairs, it's hard to see how CPV will ever make an impact. Today silicon dominates, and it is sure to do so for many years.